2025-04-14

2025-04-14导言

近几年来,数据中心,企业网络和高性能计算市场的高性能/低功耗半导体芯片组的激增,推动了互联网基础设施生态系统的巨大增长。新型创新的SerDes技术必须提供更高带宽,链路可灵活扩展和端到端信号完整性,这些要求可满足高达800G的高级网络(单通道28Gbps,56Gbps或112Gbps串行连接)的需求。

为了使这些超大规模网络成为现实,“Pathfinding”正在成为业界各路英豪们的日常任务以寻找新的设计和测试验证方法。事实上,发射器和接收器芯片组可以采用传统的眼睛张开技术,例如决策反馈均衡器(DFE),也正在尝试引入较新的方法(例如通道工作裕量(COM))来实现最快的链路。

01.

800背板设设计中的COM测量和验证方法

首先,什么是高速链路设计的“COM”?

高速链路设计的“COM”,全称:Channel Operating Margin,可翻译成通道工作裕量。“COM”是当前业界物理层设计人员早期评估开发设计空间以及优化通道物理参数的强大工具,因此可以克服眼图和BER等传统的通道性能指标分析的局限。通道工作裕量(COM),以dB表示的信噪比,它是一个相对较新的品质因数,它同时考虑了无源信道和有源信道成分。

随着数据速率超过100Gbps,通过/失败的余地变得越来越具有挑战性,开发高速数字标准的工程师认识到需要进行更多实际测试,从而使物理层信号设计工程师和通道工程师都拥有更多的设计自由。从而进入通道优化领域,进而将其转换为物理介质(插入损耗,串扰,噪声因子)的组合优化,同时实现了主动均衡(预/去加重,CTLE,DFE) 。通过为给定的物理输入迭代选择最佳均衡,COM完全适合此优化任务。

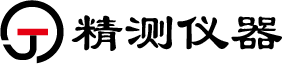

我们来看一个测试实例

图1 COM测试结果报告

那么,COM测试结果如何?

当前在讨论COM的业界标准包括以太网IEEE STD 802.3™委员会相关标准以及对光链路电气部分的光互联论坛(OIF)。

此外,当今的测试方法还是有一定局限性的,因为串行组件的附加余量通常会在更高的数据速率下产生过低的良率。通过使用COM中的高级的新概念算法以巧妙的方式更改不同组件裕量的搭配,可以在不牺牲整体通道性能的情况下提高良率和产量。

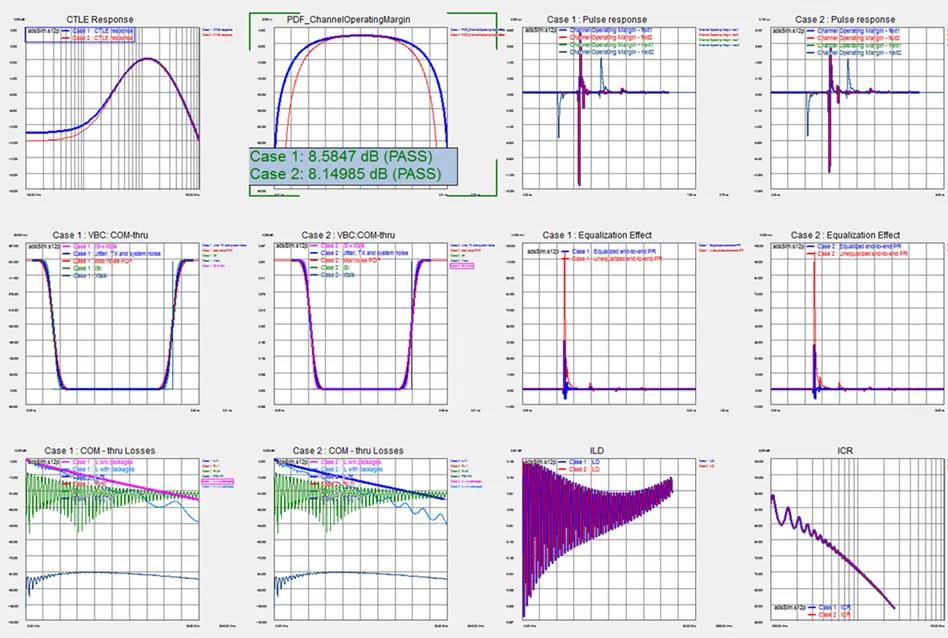

此外,可以使用数字设计人员使用的传统指标,例如眼图,如图2所示的56 Gbps PAM4眼,只要信道损耗和串扰不影响眼图张开即可。

图2 COM整体裕量分配下的56Gbps PAM-4眼图

在这种情况下,可以将眼图与COM结合使用,以权衡性能。但是,为了增加比特率,损耗和串扰,接收到的波形不会睁开眼睛,因此必须应用接收均衡(CTLE,DFE等)来实现可靠的比特接收。在后一种情况下,COM是评估通道性能的最佳方法。

02.

针对56 Gbps及以上的通道设计优化高速连接器模型

超大规模网络中使用的高速数字连接器既需要建模也需要进行相关测量的一致性评估,才能满足当今互联网基础设施对带宽的苛刻要求。

现在至关重要的是,在从子卡(Mezzanine)系统到背板互连到SERDES芯片组的整个通道中,都必须具有较高的信号完整性。与BER和眼图的传统指标相比,使用56Gbps及更高速率的新兴应用需要新的验证方法,以避免不必要地浪费通道裕量。通道工作裕量(COM)的品质因数以及测量/仿真相关性正成为设计周期的关键部分。

这篇分享文章中提出的测试案例的分析将通过提供对此类组件(作为通道的关键部分)的深入分析,来对适用于高达112 Gbps的差分互连的高速连接器进行广泛的验证。连接器模型与实验结果在时域和频域中的直通和串扰响应之间的全面相关性为后续通道设计提供了可靠的连接器模型。将COM新测试方法用于连接器模型设计,以准确预测如何以当今的超快数据速率优化信道性能。

具体来说,通过背板和铜缆进行芯片间通信的通道设计依赖于在物理和电气约束方面的多个方面的权衡。因此,必须准确预测所需的布局面积,通道长度和损耗,串扰控制以及Tx(预加重/去加重)和Rx(CTLE和DFE)SERDES的均衡方案和拓扑,以最大程度地降低成本并避免通道过度设计。

因此,应适当评估通道的设计裕度,以超过通过/失败阈值。当数据速率超过100 Gbps时(即在最新的以太网开发中,基于112 Gbps PAM4的链路),这种通道设计和优化就显得尤为重要。铜缆和背板上的芯片到芯片链接通常采用高速连接器。传输链路工程设计过程可以控制芯片的放置和扇出,以及底板互连布局直至连接器接口。

但是,设计人员在组装通道模型以评估整体性能时通常需要依赖第三方连接器数据。当需要使用外部资源时(即在连接器的情况下),可靠的通道建模以及随之而来的对其工作裕量的准确预测包括两个主要步骤。第一个是对可用数据(或模型)的验证,第二个是对连接器性能的深入分析,以确保其可靠使用。

第二篇分享文章的目的是提出一种用于速度高达112 Gbps的差分互连的高速连接器的验证。此外,深入研究了分析此类通道组件性能的关键步骤,以评估其是否可以可靠地应用于预期的通道,以通过背板进行芯片间通信。

图3 高速连接器链路架构

如要了解更多详情,请来电咨询:400-018-5117(上海精测电子有限公司);400-816-5155(深圳精测实业发展有限公司);025-58838327(南京精测国际贸易有限公司)。

------转自是德科技